## EM85F684A 682A

## USB Microcontroller

## Product Specification

Doc. Version 1.1

**ELAN MICROELECTRONICS CORP.**

March. 2018

#### **Trademark Acknowledgments:**

IBM is a registered trademark and PS/2 is a trademark of IBM. Windows is a trademark of Microsoft Corporation.

ELAN and ELAN logo are trademarks of ELAN Microelectronics Corporation.

Copyright © 2016 by ELAN Microelectronics Corporation All Rights Reserved Printed in Taiwan

The contents of in this specification are subject to change without notice. ELAN Microelectronics assumes no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN Microelectronics makes no commitment to update, or to keep current the information and material contained in this specification. Such information and material may change to conform to each confirmed order.

In no event shall ELAN Microelectronics be made responsible to any claims attributed to errors, omissions, or other inaccuracies in the information or material contained in this specification. ELAN Microelectronics shall not be liable for direct, indirect, special incidental, or consequential damages arising out of the use of such information or material. The software (if any) described in this specification is furnished under a license or nondisclosure agreement, and may be used or copied only in accordance with the terms of such agreement.

ELAN Microelectronics products are not intended for use in life support appliances, devices, or systems. Use of ELAN Microelectronics product in such applications is not supported and is prohibited.

NO PART OF THIS SPECIFICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS WITHOUT THE EXPRESS WRITTEN PERMISSION OF ELAN MICROELECTRONICS.

#### ELAN MICROELECTRONICS CORPORATION

#### Headquarters:

Hsinchu Science Park Hsinchu, TAIWAN 30076 Tel: +886 3 563-9977 Fax: +886 3 563-9966 webmaster@emc.com.tw

No. 12, Innovation 1st Road

http://www.emc.com.tw

#### Hong Kong:

## ELAN (HK) Microelectronics Corporation, Ltd.

Flat A, 19F., World Tech Centre 95 How Ming Street, Kwun Tong Kowloon, HONG KONG

Tel: +852 2723-3376 Fax: +852 2723-7780

#### Shenzhen:

## ELAN Microelectronics Shenzhen, Ltd.

8A Floor, Microprofit Building Gaoxin South Road 6 Shenzhen Hi-tech Industrial Park South Area, Shenzhen CHINA 518057 Tel: +86 755 2601-0565

Fax: +86 755 2601-0500 elan-sz@elanic.com.cn

#### USA:

#### ELAN Information Technology Group (U.S.A.)

PO Box 601 Cupertino, CA 95015 U.S.A.

Tel: +1 408 366-8225 Fax: +1 408 366-8225

#### Shanghai:

#### **ELAN Microelectronics** Shanghai, Ltd.

6F, Ke Yuan Building No. 5 Bibo Road Zhangjiang Hi-Tech Park Shanghai, CHINA 201203 Tel: +86 21 5080-3866 Fax: +86 21 5080-0273 elan-sh@elanic.com.cn

# Contents

| 1 | Gen  | eral D  | Description ······                                          | 1  |

|---|------|---------|-------------------------------------------------------------|----|

| 2 | Feat | tures · |                                                             | 2  |

| 3 | Арр  | licatio | on ·····                                                    | 4  |

| 4 | Pin  | Assig   | nment ·····                                                 | 4  |

| 5 | Pin  | Descr   | iption·····                                                 | 6  |

| 6 | Bloc | ck Dia  | gram·····                                                   | 10 |

| 7 | Fun  | ctiona  | al Description·····                                         | 11 |

|   | 7.1  |         | al Function Registers (SFR)·····                            |    |

|   |      | 7.1.1   | SFR Paging ······                                           |    |

|   |      | 7.1.2   | SFR Map ·····                                               |    |

|   | 7.2  | Stack   | ·                                                           | 14 |

|   | 7.3  | Systen  | m Clock·····                                                | 16 |

|   | 7.4  | Systen  | m Reset ·····                                               | 17 |

|   |      | 7.4.1   | Power-On Reset ·····                                        | 17 |

|   |      | 7.4.2   | Watchdog Timer Reset·····                                   | 17 |

|   |      | 7.4.3   | Software Reset·····                                         | 17 |

|   |      | 7.4.4   | Low Voltage Detector·····                                   | 17 |

|   |      | 7.4.5   | Register·····                                               | 18 |

|   | 7.5  | Operat  | tion Mode Structure·····                                    | 20 |

|   |      | 7.5.1   | Normal/Green Mode ·····                                     | 20 |

|   |      | 7.5.2   | Idle Mode ·····                                             | 21 |

|   |      | 7.5.3   | Power-Down Mode·····                                        | 21 |

|   | 7.6  | Flash I | Program Memory·····                                         | 22 |

|   |      | 7.6.1   | In-Circuit Programming (ICP)·····                           | 23 |

|   |      | 7.6.2   | In-Application Programming (IAP)······                      | 23 |

|   | 7.7  | Port C  | onfiguration ·····                                          | 23 |

|   |      | 7.7.1   | Push-Pull Output Mode · · · · · · · · · · · · · · · · · · · | 28 |

|   |      | 7.7.2   | Input-Only Mode ·····                                       | 29 |

|   | 7.8  | Interru | ıpts ·····                                                  | 30 |

|   |      | 7.8.1   | Interrupt Sources ······                                    | 30 |

|   |      | 7.8.2   | Interrupt Priority ······                                   | 36 |

|   |      | 7.8.3   | INT PIN ·····                                               | 40 |

|   |      | 7.8.4   | Pin-Change ·····                                            |    |

|   | 7.9  | Watch   | dog Timer (WDT)·····                                        | 45 |

|   | 7.10 | Periph  | neral Power Down ·····                                      | 47 |

|      | Universal Serial Bus (USB) ······                                                             |     |

|------|-----------------------------------------------------------------------------------------------|-----|

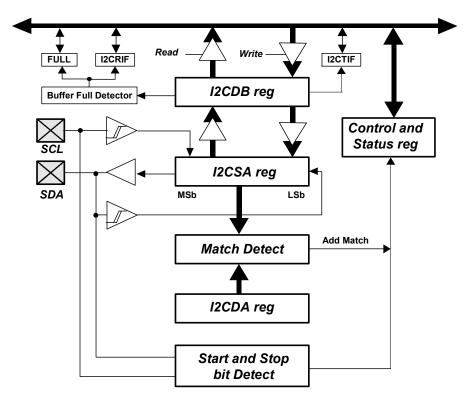

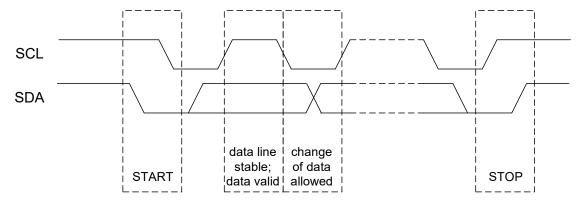

| 7.12 | I <sup>2</sup> C (Inter-Integrated Circuit) ······                                            | 67  |

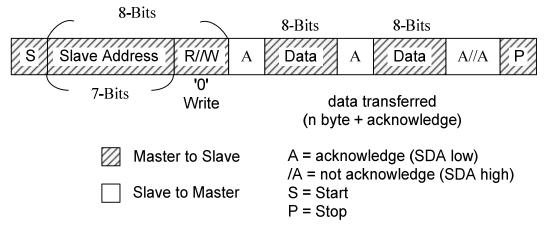

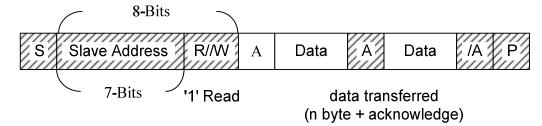

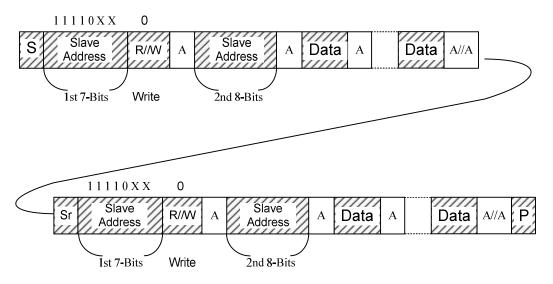

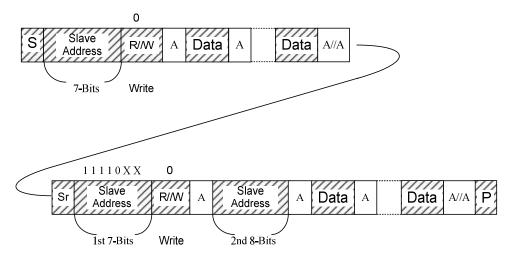

|      | 7.12.1 7-Bit Slave Address ······                                                             | 68  |

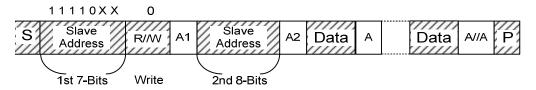

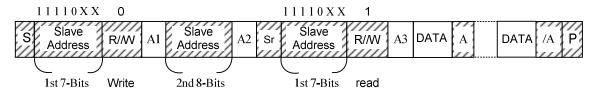

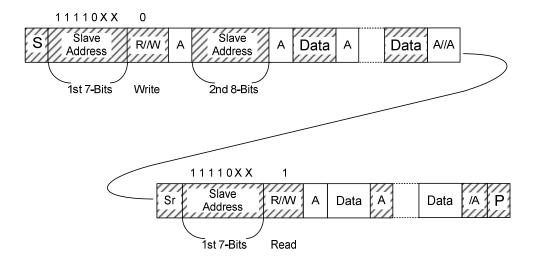

|      | 7.12.2 10-Bit Slave Address ·····                                                             | 69  |

|      | 7.12.3 I2CB Register · · · · · · · · · · · · · · · · · · ·                                    | 73  |

| 7.13 | UART······                                                                                    | 83  |

|      | 7.13.1 UART Mode 0: Synchronous ······                                                        | 83  |

|      | 7.13.2 UART Mode 1: 8-bit UART (Variable Baud Rate)·····                                      |     |

|      | 7.13.3 UART Mode 2: 9-bit UART (Fixed Baud Rate)                                              | 84  |

|      | 7.13.4 UART Mode 3: 9-BIT UART (Variable Baud Rate) ······                                    | 85  |

|      | 7.13.5 UART Baud Rates                                                                        | 85  |

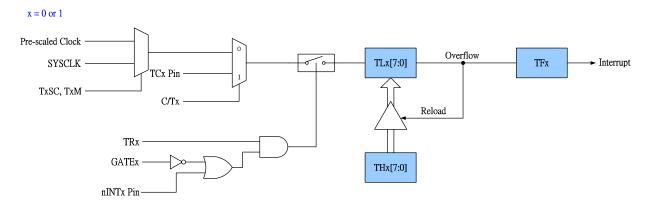

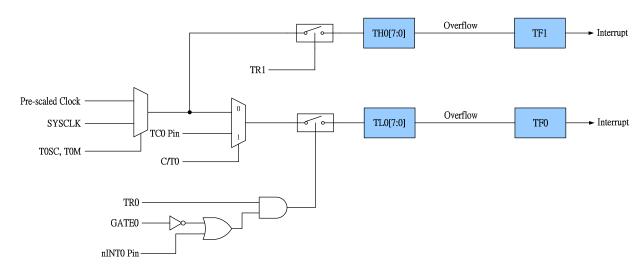

| 7.14 | Timer                                                                                         |     |

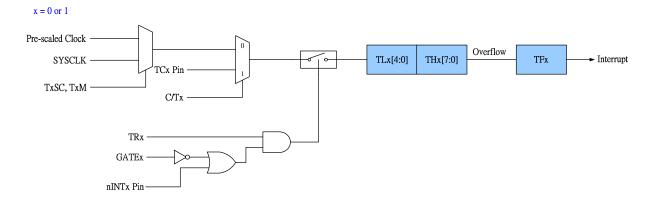

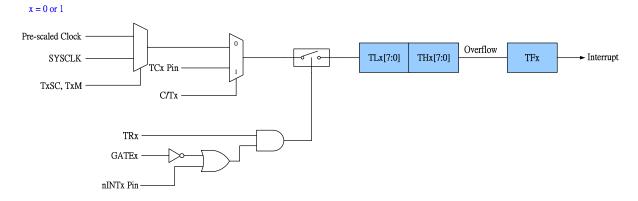

|      | 7.14.1 Timer 0 and Timer 1 ······                                                             |     |

|      | 7.14.1.1 Timer 0/1 Mode 0: 13-bit Counter/Timer·····                                          |     |

|      | 7.14.1.2 Timer 0/1 Mode 1: 16-bit Counter/Timer·····                                          |     |

|      | 7.14.1.3 Timer 0/1 Mode 2: 8-bit Counter/Timer with Auto-Reload ·······                       |     |

|      | 7.14.1.4 Timer 0 Mode 3 Two 8-bit Counter/Timers ······                                       | 90  |

|      | 7.13.2 Timer 3 Register ······                                                                |     |

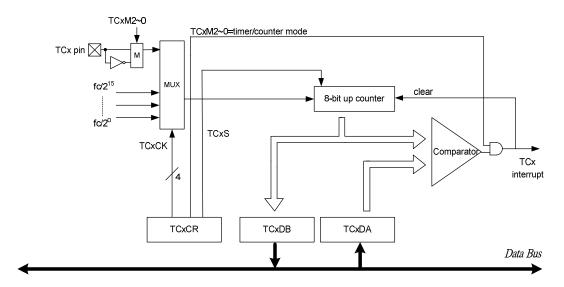

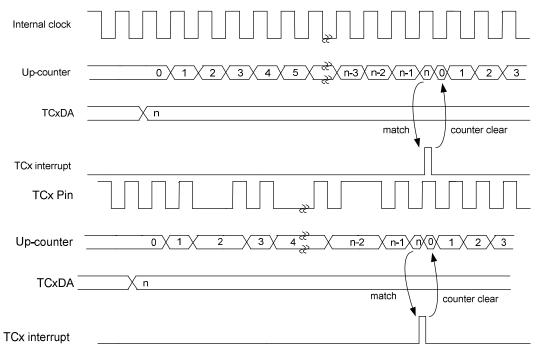

| 7.15 | PWM                                                                                           |     |

|      | 7.15.1 Increment Timer Counter (TMRX)······                                                   |     |

|      | 7.15.2 PWM Time Period (PRDX)                                                                 |     |

|      | 7.15.3 PWM Duty Cycle (DTX)·······                                                            |     |

|      | 7.15.4 PWM Programming Process/Steps ·······                                                  |     |

|      | 7.15.5 PWM Register ······                                                                    | 101 |

| 7.16 | SPI                                                                                           |     |

|      | 7.16.1 SPI Signal · · · · · · · · · · · · · · · · · · ·                                       |     |

|      | 7.16.1.1 Serial Clock (SCK)·····                                                              |     |

|      | 7.16.1.2 Master Data Out Slave Data-In (MOSI)·····                                            |     |

|      | 7.16.1.3 Master Data in Slave Data Out (MISO)                                                 |     |

|      | 7.16.1.4 Slave Select (/SS)······                                                             | 120 |

|      | 7.16.2 SPI Transfer Format ····································                               |     |

|      | 7.16.3 Shift Data Register (SPISFDR) ····································                     |     |

|      | 7.16.4 Operations                                                                             |     |

|      | 7.16.4.1 Master Mode Operation ······                                                         |     |

|      | 7.16.4.2 Slave Mode Operation ······                                                          |     |

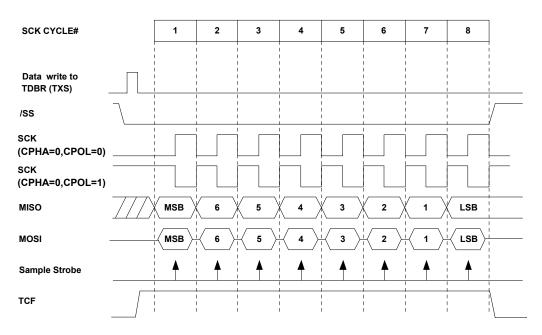

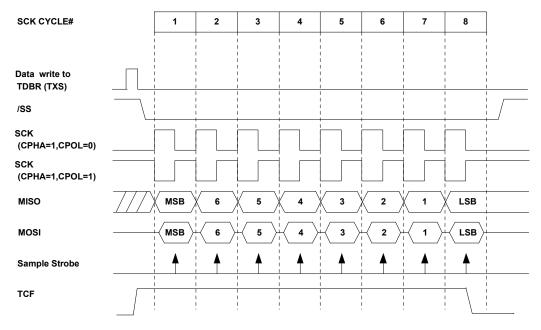

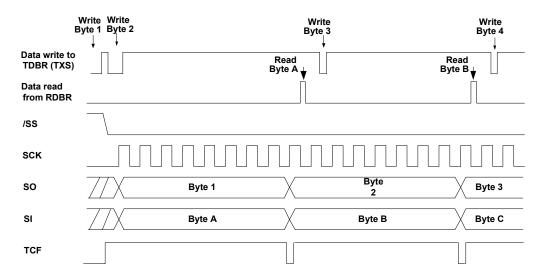

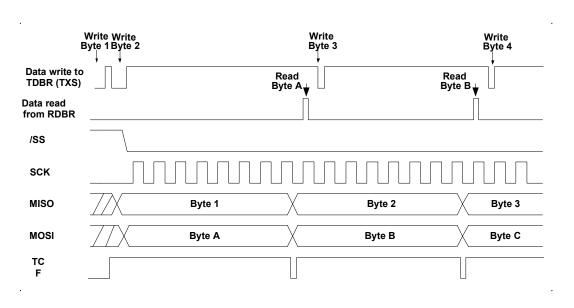

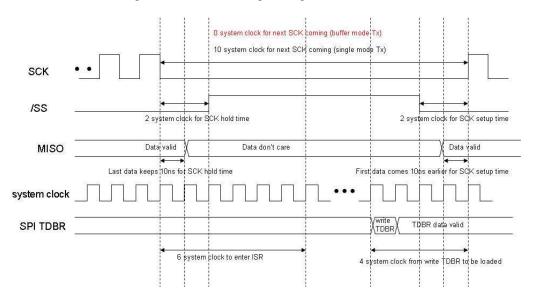

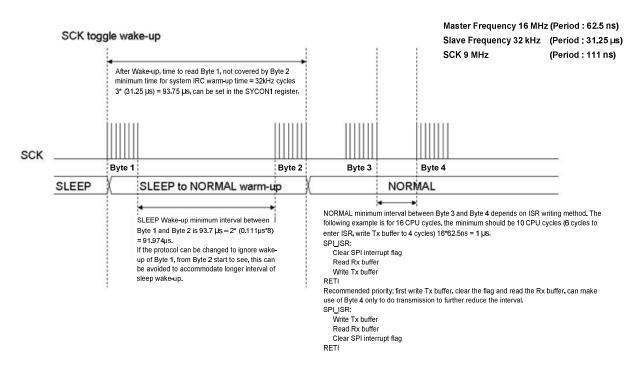

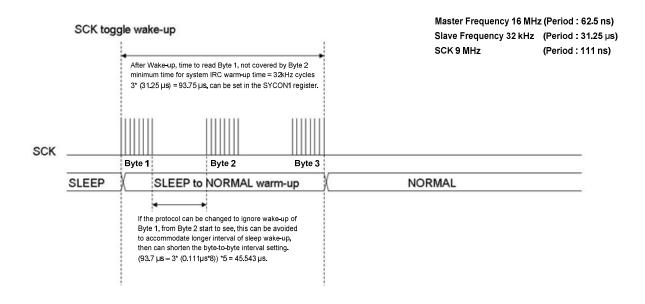

|      | 7.16.5 Timing Diagram ····································                                    |     |

|      | 7.16.5.1 SPI Master Mode······                                                                |     |

|      | 7.16.5.2 SPI Slave Mode Timing (CPHA=1 / CHPA=0) ······                                       |     |

|      | 7.16.5.3 Consecutively Receiving Bytes (CPHA=1 / CHPA=0) ···································· |     |

|      | 7.16.5.4 SPI Slave Timing Requirement ····································                    |     |

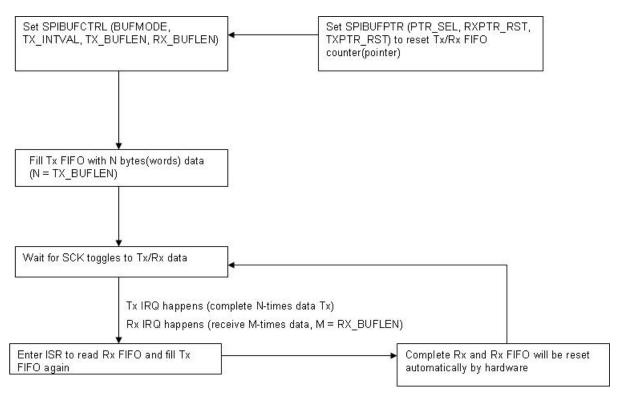

|      | 7.16.6 Buffer mode function·······                                                            |     |

|      | 7.16.7 SPI Register                                                                           |     |

| 7.17 |                                                                                               |     |

| 7.17 |                                                                                               |     |

| 7.10 | 7.18.1 Limitations of On-Chip Debug ·······                                                   |     |

| 7 19 | Code Option ······                                                                            |     |

|      |                                                                                               | .00 |

| Ì  | OLAN                                 | Contents  |

|----|--------------------------------------|-----------|

|    | 7.20 CPU Register Descriptions       | ······141 |

| 8  | Absolute Maximum Ratings ······      | 149       |

| 9  | DC Electrical Characteristics ······ | 150       |

| 10 | ) Power Sequence·····                | 152       |

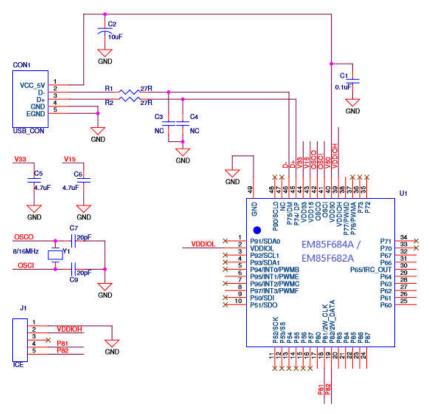

|    | 1 Application Circuit ······         |           |

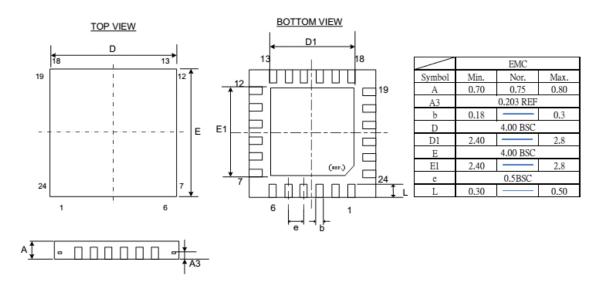

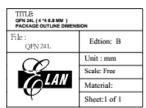

| 12 | 2 Package Information ·····          | 154       |

## Specification Revision History

|         | -                                     |            |  |  |  |  |

|---------|---------------------------------------|------------|--|--|--|--|

| Version | Revision Description                  |            |  |  |  |  |

| 1.0     | Preliminary version                   | 2018/04/02 |  |  |  |  |

| 1.1     | Modify EPOUTPREHOLD & EPINPREHOLD bit | 2018/05/07 |  |  |  |  |

| 1.1     | Modify Application Circuit            | 2010/03/01 |  |  |  |  |

### 1 General Description

EM85F684A/EM85F682A is a high-performance Flash version of the 80C52 single-chip 8-bit microcontroller with full speed USB functions.

EM85F684A/EM85F682A features a full-speed USB module compatible with the USB specifications Version 2.0. This module integrates the USB transceivers with a 3.3V voltage regulator and the Serial Interface Engine (SIE). USB Event detection logic (Reset and Suspend/Resume) and FIFO buffers supporting the mandatory control Endpoint (EP0) and up to four versatile Endpoints (EP1/EP2/EP3/EP4) with minimum software overhead are also part of the USB module. EM85F684A/EM85F682A retains the features of the 80C52 with 256 bytes RAM, 2048/1024 bytes XRAM, two 16-bit Timers/Counters (T0/T1), a full duplex UART and an on-chip oscillator. EM85F684A/EM85F682A also has built-in peripheral functions such as SPI, two I2C, 6 PWMs, etc.

#### 2 Features

- Operating Voltage:

- USB: 4.25V ~ 5.5V at 0°C~70°C (commercial)

- Non-USB: 3V ~ 5.5V at 0°C ~70°C (commercial)

- Memory Configuration:

- Flash ROM size:

- ◆ EM85F684A: 32K x 8 bits (Including ISP boot code 8K bytes)

- ◆ EM85F682A: 16K x 8 bits (Including ISP boot code 8K bytes)

- 2K x 8 bits for EEPROM

- ♦ EM85F684A: When use EEPROM function, Flash ROM size = 30K x 8 bits.

- ◆ EM85F682A: When use EEPROM function, Flash ROM size = 16K x 8 bits.

- 10,000 write/erase cycles

- More than 10 years data retention

- RAM:

- ♦ EM85F684A: 2048 x 8 bits XRAM / EM85F682A: 1024 x 8 bits XRAM

- ◆ 256 x 8 bits RAM

- ◆ USB FIFO: 320 bytes (64 bytes for EP0 and 256 bytes for EP1~EP4).

- USB Specification Compliance:

- Full-speed Universal Serial Bus Specification Version 2.0.

- P75 (D+) has an internal pull-high resistor (1.5 KΩ).

- 1 Control Endpoint (EP0).

- 4 Bulk/Interrupt/Isochronous Endpoint (EP1~EP4).

- Programmable EP1~EP4 FIFO depth.

- I/O Ports

- Each GPIO pin of Ports 5, 6, 7, 8, 9, has an internal programmable pull-high resistor.

- Pin change wakeup: Ports 5, 6, 9

- Output Ports have high drive/sink mode

- Interrupt:

- Internal: TIMER0/1, Timer3, WDT, I2CA/B, SPI, PWMA /B/C/D/E/F, USB, UART

- External: INT0~INT3, I/O pin change interrupt

- Two 16-bit Timer Counters: T0/T1

- One 8-bit Timer: T3

- Operation Frequency:

- XTAL Mode: 8/16 MHz

- PLL24M: Source Clock From XTAL 8/16MHz.

- Internal High RC Mode: 8/16/24 MHz

- Internal Low RC Mode: 256K/32K/4K/500Hz

- Operation Mode:

- Normal Mode: Both high clock and low clock active.

- Green Mode: Low clock only

- Idle Mode: CPU clock halt, peripheral clock still in oscillation.

- Power-Down Mode: Both high clock and low clock stop.

- Serial Peripheral Interface (SPI)

- 4-wire synchronous with 8-byte buffer

- 2~12 MHz Master/Slave

- Two sets Inter-Integrated Circuit (I2CA/I2CB).

- Master/Slave with 7/10 bits address and 8 bits data transmit/receive.

- Baud rate: 400k/100kbps.

- Six sets Pulse Width Modulation (PWM).

- Maximum: 6 channels PWM output.

- 16-bit resolution PWM output.

- Package Type:

- ◆ 48-pin QFN (5 x 5 x 0.6mm) EM85F684AAW / EM85F682AAW

- ◆ 24-pin QFN (4 x 4 x 0.8mm) EM85F684ADW

## 3 Application

**USB** Gamming Keyboard

**USB Joystick**

**USB** Docking

**USB Docking+ Battery Charger**

### 4 Pin Assignment

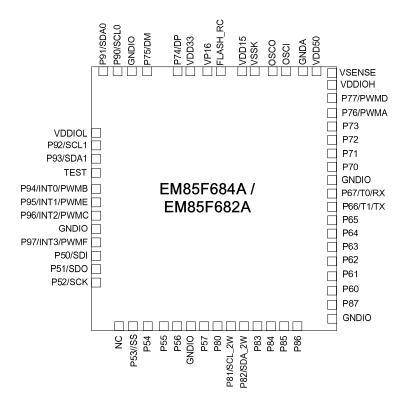

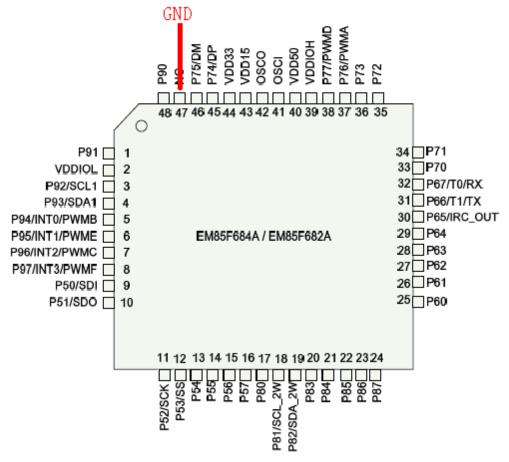

Figure 4-1 DIE

(The Test pin must be bonded to the ground)

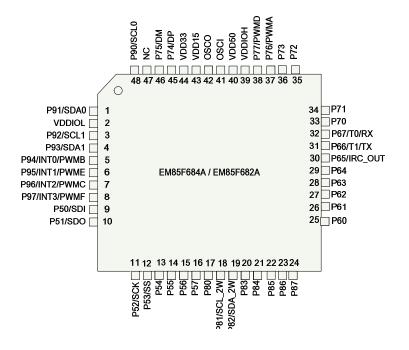

Figure 4-2 EM85F684A/EM85F682A QFN48 (5\*5\*0.6mm)

## 5 Pin Description

| Name           | Function      | Input<br>Type | Description                                                                                       |

|----------------|---------------|---------------|---------------------------------------------------------------------------------------------------|

| VDD50          | VDD           | Power         | Power supply input pins for digital, analog and USB circuit.                                      |

| VDD50A         | VDD           | Power         | Power supply input pins for analog circuit.                                                       |

| VDD15          | V1p5          | Power         | V1.5 output                                                                                       |

| VDD33          | V33           | Power         | V33 output (Provide P74/75, P90/91 power)                                                         |

| VSS            | Vss           | -             | Ground input. The package substrate must be connected to Ground.                                  |

| VDDIOH         | I/O VDD       | Power         | Power supply input pins for the I/O power (P5/6/P70~73,76,77/P8, P94~97 I/O power input)          |

| VDDIOL         | I/O VDD       | Power         | Power supply input pins for the I/O power of P92, P93                                             |

| VSSK           | VSS           | Power         | Kernel Ground                                                                                     |

| GNDIO          | I/O<br>Ground | Power         | I/O Ground                                                                                        |

| GNDA           | GNDA          | Power         | Analog and USB Ground                                                                             |

| OSCI           | OSCI          | I             | Crystal input                                                                                     |

| OSCO           | osco          | 0             | Crystal output                                                                                    |

| P50/SDI (MOSI) | P50           | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor.             |

|                | DSI           | ST            | SPI serial data input.                                                                            |

| P51/SDO(MISO)  | P51           | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor.             |

| , ,            | SDO           | ST            | SPI serial data output                                                                            |

| P52/SCK        | P52           | ST            | Bi-directional I/O pin with programmable pull-down, pull-high, open-drain, and pin change wake-up |

|                | SCK           | ST            | SPI serial clock input/output                                                                     |

| P53//SS        | P53           | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor.           |

|                | SS            | ST            | SPI slave mode enable                                                                             |

| P54            | P54           | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor            |

| P55            | P55           | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor            |

| P56            | P56           | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor            |

| P57            | P57           | ST            | Bi-directional pin. Schmitt trigger structure as input<br>mode. Built-in pull-up resistor         |

| Name         | Function                                                  | Input<br>Type | Description                                                                                                 |  |  |  |  |

|--------------|-----------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P60          | P60                                                       | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |  |  |  |  |

| P61          | P61                                                       | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |  |  |  |  |

| P62          | P62                                                       | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |  |  |  |  |

| P63          | Bi-direction nin. Schmitt trigger structure as input mode |               |                                                                                                             |  |  |  |  |

| P64          | P64                                                       | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |  |  |  |  |

|              | P65                                                       |               | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |  |  |  |  |

| P65/ IRC_OUT | IRC_OUT                                                   | ST            | IRC clock output pin                                                                                        |  |  |  |  |

|              | RESET                                                     | ST            | Hardware Reset Pin. Select from Code Option 3.                                                              |  |  |  |  |

|              | P66                                                       | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |  |  |  |  |

| P66          | T1                                                        | ST            | T1 external input pin                                                                                       |  |  |  |  |

| . ••         | TX                                                        | ST            | UART TX port                                                                                                |  |  |  |  |

|              | RESET                                                     | ST            | Hardware Reset Pin. Select from Code Option 3.                                                              |  |  |  |  |

|              | P6V7                                                      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |  |  |  |  |

| P67          | T0                                                        | ST            | T0 external input pin                                                                                       |  |  |  |  |

|              | RX                                                        | ST            | UART RX port                                                                                                |  |  |  |  |

| P70          | P70                                                       | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                      |  |  |  |  |

| P71          | P71                                                       | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                      |  |  |  |  |

| P72          | P72                                                       | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                      |  |  |  |  |

| Name          | Function | Input<br>Type | Description                                                                                                                    |

|---------------|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------|

| P73           | P73      | ST            | Bi-direction pin. Schmitt trigger structure as input mode.<br>Built-in pull-up resistor                                        |

| P74/ DP       | P74      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor (3.3V IO)                                 |

|               | DP       | ST            | USB Differential D+ signal line.                                                                                               |

| P75/DM        | P75      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor (3.3V IO)                                 |

|               | DM       | ST            | USB Differential D- signal line.                                                                                               |

| P76 / PWMA    | P76      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                                           |

|               | PWMA     | ST            | Pulse width modulation output A.                                                                                               |

| P77 / PWMD    | P77      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                                           |

|               | PWMD     | ST            | Pulse width modulation output D.                                                                                               |

| P80           | P80      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                                           |

| 1 00          | USB IAP  | ST            | USB IAP pin. Input pull-high, when this pin is low level voltage after power on, entry boot code mode.                         |

| P81 / 2W_CLK  | P81      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor  UBRG debug pin , this pin must set input |

|               | 2W_CLK   | ST            | OCD clock line.                                                                                                                |

| P82 / 2W_DATA | P82      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor  UBRG debug pin , this pin must set input |

|               | 2W_DATA  | ST            | OCD data line.                                                                                                                 |

| P83           | P83      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                                           |

| P84           | P84      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                                           |

| P85           | P85      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                                           |

| Name          | Function | Input<br>Type | Description                                                                                                      |

|---------------|----------|---------------|------------------------------------------------------------------------------------------------------------------|

| P86           | P86      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                             |

| P87           | P87      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor                             |

|               | P90      | ST            | 3.3V Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |

| P90           | SCL0     | ST            | I <sup>2</sup> CA serial clock line. It is open-drain.                                                           |

|               | RESET    | ST            | Hardware Reset Pin. Select from Code Option 3.                                                                   |

| P91           | P91      | ST            | 3.3V Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up |

|               | SDA0     | ST            | I <sup>2</sup> CA serial data line. It is open-drain                                                             |

| P92/SCL1      | P92      | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up    |

|               | SCL1     | ST            | I2CB serial clock line. It is open-drain.                                                                        |

| P93/SDA1      | P93      | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up    |

|               | SDA1     | ST            | I2CB serial data line. It is open-drain                                                                          |

|               | P94      | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up    |

| P94/INT0/PWMB | INT0     | ST            | External interrupt pin.                                                                                          |

|               | PWMB     | ST            | Pulse width modulation Output B.                                                                                 |

|               | P95      | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up    |

| P95/INT1/PWME | PWME     |               | Pulse width modulation Output E.                                                                                 |

|               | INT1     | ST            | External interrupt pin.                                                                                          |

|               | P96      | ST            | Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up      |

| P96/INT2/PWMC | INT2     | ST            | External interrupt pin.                                                                                          |

|               | PWMC     | ST            | Pulse width modulation output C.                                                                                 |

|               | RESET    | ST            | Hardware Reset Pin. Select from Code Option 3.                                                                   |

|               | P97      | ST            | Bi-directional pin. Schmitt trigger structure as input mode. Built-in pull-up resistor and pin change wake-up    |

| P97/INT3/PWMF | INT3     | ST            | External interrupt pin.                                                                                          |

|               | PWMF     | ST            | Pulse width modulation Output F.                                                                                 |

Note: P81 and 82 are UBRG debug pins, user must set these two pins as input floating when using OCD debug.

## 6 Block Diagram

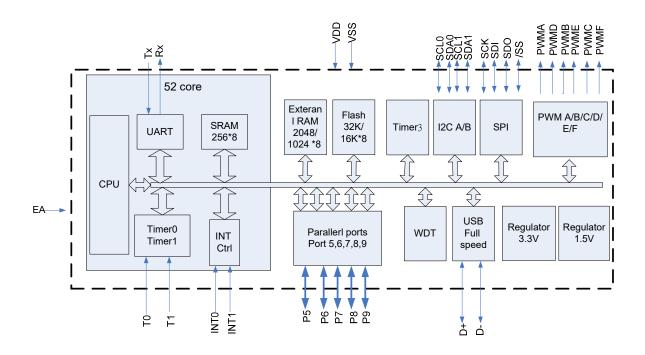

Figure 6-1 EM85F684A/682A Functional Block Diagram

#### 7 Functional Description

#### 7.1 Special Function Registers (SFR)

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 are bit-addressable as well as byte-addressable.

#### 7.1.1 SFR Paging

EM85F684A/EM85F682A implements a 'paged' SFR scheme which can expand the number of available SFR addresses, user can switch SFR page by setting PAGESW register (0x86) Bit 0.

#### **PAGESW: Page Switch**

| Bit   | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0    |

|-------|----------|----------|----------|----------|----------|----------|----------|------|

| NI    | D        | D        |          |          | D        | D        | D        | PAGE |

| Name  | Reserved | SW.0 |

| Туре  | R/W      | R/W  |

| Reset | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0    |

SFR Address = 0x86; SFR Page = All Pages

#### 7.1.2 SFR Map

| PAGE0     | 0(8)  | 1(9)    | 2(A)    | 3(B)       | 4(C)       | 5(D)    | 6(E)    | 7(F)    |

|-----------|-------|---------|---------|------------|------------|---------|---------|---------|

| F8        | -     | P5M0    | P6M0    | P7M0       | P8M0       | PHCON0  | -       | PHDSC0  |

| F0        | В     | -       | -       | -          | -          | PHCON1  | -       | PHDSC1  |

| E8        | P9    | 1       | 1       | -          | -          | -       | WDTKEY  | WDTCR   |

| E0        | ACC   | I2CBCR4 | 1       | -          | -          | -       | 1       | -       |

| D8        | PSW1  | I2CBCR1 | I2CBCR2 | I2CBSA     | I2CBDB     | I2CBDAL | I2CBDAH | I2CBCR3 |

| D0        | PSW0  | 1       | 1       | -          | -          | -       | 1       | I2CBINT |

| C8        | 1     | 1       | 1       | LVDCR      | LVDCR1     | DEVPD1  | DEVPD2  | DEVPD3  |

| C0        | RSTSC | RSTSC   | I2CACR1 | I2CACR2    | I2CASA     | I2CADB  | I2CADAL | I2CADAH |

| В8        | IP    | EIP1    | EIP2    | EIP3       | -          | PRST    | 1       | -       |

| В0        | P8    | EIE1    | EIE2    | EIE3       | -          | EXEN    | EIESC1  | EIESC2  |

| <b>A8</b> | ΙE    | TC3CR1  | TC3CR2  | TC3DA      | TC3DB      | -       | ICEN    | EEXSF   |

| Α0        | P7    | SPICON1 | SPICON2 | SPITDBR    | SPIRDBR    | SPISR1  | SPISR2  | SPITX   |

| 98        | SCON  | SBUF    | SPIRX   | SPIBUFPTR1 | SPIBUFPTR2 | -       | -       | -       |

| 90        | P6    | -       | -       | -          | -          | -       | -       | XPAGE   |

| 88        | TCON  | TMOD    | TL0     | TL1        | TH0        | TH1     | CKCON0  | CKCON1  |

| 80        | P5    | SP      | DPL     | DPH        | DPL1       | DPH1    | PAGESW  | PCON    |

Figure 7.1.1 SFR Memory Map in Page 0

| PAGE1      | 0 (8) | 1 (9)                | 2 (A)              | 3 (B)              | 4 (C)              | 5 (D)              | 6 (E)          | 7 (F)         |

|------------|-------|----------------------|--------------------|--------------------|--------------------|--------------------|----------------|---------------|

| F8         | -     | P9M0                 | -                  | -                  | -                  | PHCON2             | -              | PHDSC2        |

| F0         | В     | PWMCCR               | PRDCL              | PRDCH              | DTCL               | DTCH               | TMRCL          | TMRCH         |

| E8         | P9    | PWMBCR               | PRDBL              | PRDBH              | DTBL               | DTBH               | TMRBL          | TMRBH         |

| E0         | ACC   | PWMACR               | PRDAL              | PRDAH              | DTAL               | DTAH               | TMRAL          | TMRAH         |

| D8         | PSW1  | -                    | USBCTRL            | -                  | -                  | -                  | PWMTER         | PWMSF         |

| D0         | PSW0  | UDCEP4DA<br>TAOUTCNT | UDCEP1B<br>UFDEPTH | UDCEP2B<br>UFDEPTH | UDCEP3B<br>UFDEPTH | UDCEP4B<br>UFDEPTH | PHYTEST0       | -             |

| C8         |       | UDCEP1DA             | UDCEP1DA           | UDCEP2DA           | UDCEP2DA           | UDCEP3DA           | UDCEP3DA       | UDCEP4DA      |

| Co         | -     | TAINCNT              | TAOUTCNT           | TAINCNT            | TAOUTCNT           | TAINCNT            | TAOUTCNT       | TAINCNT       |

| CO         | RSTSC | UDCEP1B<br>UFDATA    | UDCEP2B<br>UFDATA  | UDCEP3B<br>UFDATA  | UDCEP4B<br>UFDATA  | UDCBUFST<br>A      | -              | -             |

| <b>D</b> 0 | i     | UDCINT0S             | UDCINT1S           | UDCINT2S           | UDCEPCT            | UDCEPBU            | UDCEPBU        | UDCEP0B       |

| B8         | IP    | TA                   | TA                 | TA                 | RL                 | FCTRL0             | FCTRL1         | UFDATA        |

| В0         | P8    | UDCCTRL              | UDCSTA             | UDCCFSTA           | UDCCFDAT<br>A      | UDCINT0E<br>N      | UDCINT1E<br>N  | UDCINT2E<br>N |

| A8         | ΙE    | -                    | -                  | -                  | -                  | -                  | -              | -             |

| Α0         | P7    | -                    | -                  | -                  | -                  | -                  | -              | -             |

| 98         | SCON  | SBUF                 | UDCEPBU            | UDCEPBU            | UDCEPBU            | STDCMDF            | -              | -             |

| 90         | P6    | -                    | FCTRL2<br>-        | FCTRL3             | FCTRL4<br>-        | LG<br>EEPCTRL      | EEPAREAS<br>EL | -             |

| 88         | TCON  | TMOD                 | TL0                | TL1                | TH0                | TH1                | CKCON0         | CKCON1        |

| 80         | P5    | SP                   | DPL                | DPH                | DPL1               | DPH1               | PAGESW         | PCON          |

Figure 7.1.2 SFR Memory Map in Page 1

| PAGE2 | 0 (8) | 1 (9)    | 2 (A)    | 3 (B)    | 4 (C)    | 5 (D)    | 6 (E)    | 7 (F)   |

|-------|-------|----------|----------|----------|----------|----------|----------|---------|

| F8    | ı     | -        | -        | -        | -        | -        | -        | -       |

| F0    | В     | PWMFCR   | PRDFL    | PRDFH    | DTFL     | DTFH     | TMRFL    | TMRFH   |

| E8    | P9    | PWMECR   | PRDEL    | PRDEH    | DTEL     | DTEH     | TMREL    | TMREH   |

| E0    | ACC   | PWMDCR   | PRDDL    | PRDDH    | DTDL     | DTDH     | TMRDL    | TMRDH   |

| D8    | PSW1  | -        | -        | -        | -        | -        | PWMTER1  | PWMSF1  |

| D0    | PSW0  | -        | -        | -        | -        | -        | -        | -       |

| C8    | -     | -        | -        | -        | -        | -        | -        | -       |

| CO    | RSTSC | -        | -        | •        | -        | ı        | ı        | -       |

| В8    | IP    | UDCEP1AB | UDCEP2AB | UDCEP3AB | UDCEP4AB | UDCINT4E | UDCINT4S |         |

| БО    |       | UFDATA   | UFDATA   | UFDATA   | UFDATA   | N        | TA       | -       |

| В0    | P8    | UDCINT3E | UDCINT3S | UDCEPBU  | UDCEPBU  | UDCEPBU  | UDCEPBU  | UDCEPBU |

| В     | го    | N        | TA       | FCTRL5   | FCTRL6   | FCTRL7   | FCTRL8   | FCTRL9  |

| A8    | ΙE    | -        | -        | -        | -        | -        | -        | -       |

| Α0    | P7    | -        | -        | -        | -        | -        | -        | -       |

| 98    | SCON  | SBUF     | -        | -        | -        | -        | -        | -       |

| 90    | P6    | -        | -        | -        | -        | -        | -        | -       |

| 88    | TCON  | TMOD     | TL0      | TL1      | TH0      | TH1      | CKCON0   | CKCON1  |

| 80    | P5    | SP       | DPL      | DPH      | DPL1     | DPH1     | PAGESW   | PCON    |

Figure 7.1.3 SFR Memory Map in Page 2

#### 7.2 Stack

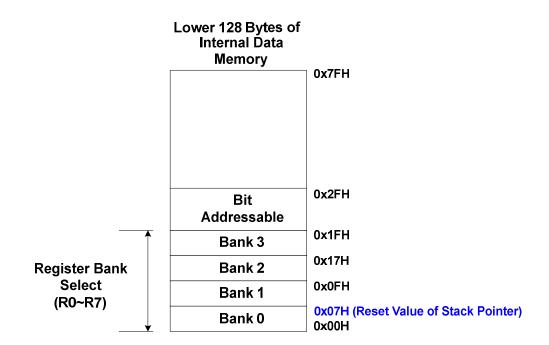

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. (The Stack Pointer is incremented before data is stored during PUSH and CALL execution and decremented after data is popped during POP, RET and RETI execution) A reset initializes the stack pointer to Location 0x07, as shown in Figure 7.2.1. Therefore, the first value pushed on the stack is placed at Location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

Figure 7.2.1 Stack Pointer Reset Value

#### **SP: Stack Pointer**

| Bit   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|------|------|------|------|------|------|

| Name  | SP.7 | SP.6 | SP.5 | SP.4 | SP.3 | SP.2 | SP.1 | SP.0 |

| Туре  | R/W  |

| Reset | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    |

SFR Address = 0x81; SFR Page = All Pages

#### 7.3 System Clock

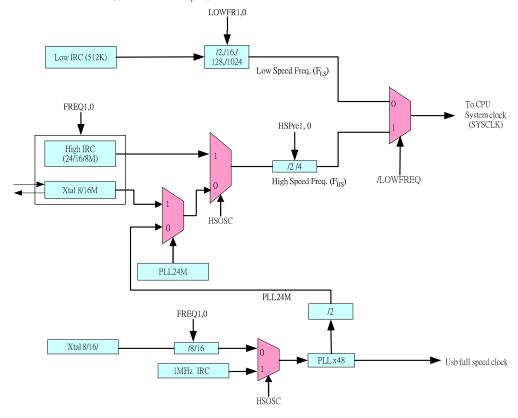

- EM85F684A/EM85F682A is a dual clock system including high-speed and low-speed clocks. The high-speed clock includes internal high-speed oscillator and external oscillators selected by "FSOSC" code option. The low-speed clock is from internal low-speed oscillator controlled by "LOWFR1,0" bit of CKCON1 register. Both high-speed clock and low-speed clock can be system clock source.

- High Speed clock source:

- 1. External 8/16MHz Crystal

- 2. Internal 8/16/24 MHz RC Oscillator (default)

- 3. PLL24MHz: Clock source from External 8/16MHz Crystal.

- Low speed clock:

Internal RC Oscillator 512kHz divide to 500Hz/4K/32K/256kHz for CPU clock

- Peripherals clock source:

- UART/ Time0&1/SPI: System clock

- I2C: FHS

- Timer3/ PWM: FHS, F512kHz

Figure 7.3.1 Clock system

#### 7.4 System Reset

When entering the Reset state, the CPU stop operating and the Interrupt and Timer are disabled, System Reset all of SFR are initialized to the default value, the Program Counter (PC) is reset, the program is executed by the Reset Vector (0000H), during the Reset period, the internal data memory content does not change (stored data before Reset will remain unchanged), all I/O registers are set to an initial value (I/O as the Default mode). EM85F684A/EM85F682A has three sources of reset: power-on reset, watchdog reset and software reset.

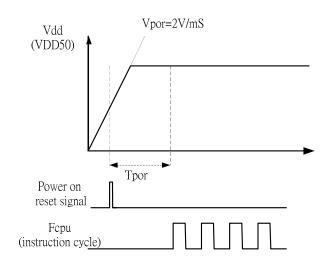

#### 7.4.1 Power-On Reset

Power-On Reset (POR) during power-up will carry out System Reset. The CPU will stop operating and maintain the Reset state until VDD rises to above POR voltage. When VDD drops to below POR voltage then it will again carry out Reset System to return to the Reset state, but a POR occurs and PORSF (RSTSC.0) will be set to 1, it can help user to confirm whether to start operating from the next CPU Power-On condition. PORSF bit is set by hardware, cleared by Software.

#### 7.4.2 Watchdog Timer Reset

When WDT is enabled to start the counter, WTSF will be set by WDT overflow. If WDTE (WDTCR.7) is enabled, the WDT overflow will force a system reset that causes CPU to restart. After exiting from reset status, the software can read the WTSF to recognize that WDT reset occurred. For WDT details, refer to Section 10 Watchdog Timer. Note that when POR occurs, WTSF will be cleared.

#### 7.4.3 Software Reset

The SWRSF (RSTSC.7) is set to 1 will force to generate a System Reset, when Reset is caused by a Software Reset, after exiting the Reset state, SWRSF (RSTSC.7) is set to 1. Note that when POR occurs, SWRSF will be cleared.

#### 7.4.4 Low Voltage Detector

Under unstable power source condition, such as external power noise interference or EMS test condition, a violent power vibration could occur. At the time, the VDD could become unstable as it could be operating below working voltage. When the system supply voltage (VDD) is below operating voltage, the IC kernel will automatically keep all register status  $\circ$

#### 7.4.5 Register

**RSTSC: Reset Source**

| Bit   | 7      | 6 | 5 | 4 | 3 | 2      | 1 | 0      |

|-------|--------|---|---|---|---|--------|---|--------|

| Name  | SWRSF  | - | - | - | - | WTSF   | ı | PORSF  |

| Type  | R/W    | R | R | R | R | R/W    | R | R/W    |

| Reset | Varies | 0 | 0 | 0 | 0 | Varies | 0 | Varies |

SFR Address = 0xC0; SFR Page = All Pages

Bit 7: Software Reset Force and Flag.

Write:

0: No effect

1: System reset

Read:

0: No software reset that occurs.

1: Software reset caused a system reset.

Bits 6~4, 1, 3: Reserved. Read = 0, Write = Don't Care.

Bit 2: Watchdog Reset Flag.

Set to 1 if a watchdog reset occurs. It must be cleared by software.

Bit 0: Power-On Flag.

Set to 1 anytime a power-on occurs. It must be cleared by software.

#### P: Previous status before reset

| B 1 E 1        | Reset Flag |      |       |  |  |  |  |

|----------------|------------|------|-------|--|--|--|--|

| Reset Event    | SWRSF      | WTSF | PORSF |  |  |  |  |

| Power-On Reset | 0          | 0    | 1     |  |  |  |  |

| Watchdog Reset | Р          | 1    | Р     |  |  |  |  |

| Software Reset | 1          | Р    | Р     |  |  |  |  |

| OCD Reset      | 0          | 0    | 1     |  |  |  |  |

Table 7.4 Reset Flag Status after Reset Event Occur

#### **PRST: Peripheral Reset**

| Bit   | 7 | 6 | 5 | 4 | 3       | 2      | 1       | 0       |

|-------|---|---|---|---|---------|--------|---------|---------|

| Name  | 1 | 1 | I | I | UARTRST | SPIRST | I2CBRST | I2CARST |

| Туре  | R | R | R | R | R/W     | R/W    | R/W     | R/W     |

| Reset | 0 | 0 | 0 | 0 | 0       | 0      | 0       | 0       |

SFR Address = 0xBD; SFR Page = 0

**Bit 3: UART reset bit.** Reset UART registers and pin state as default, initialize state of the machine.

Bit 2: SPI reset bit. Reset SPI registers and pin state as default, initialize state of the machine.

**Bit 1: I2CB reset bit.** Reset I2CB registers and pin state as default, initialize state of the machine.

**Bit 0: I2CA reset bit.** Reset I2CA registers and pin state as default, initialize state of the machine.

#### **LVDCR: LVD Control Register**

| Bit   | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---|---|---|---|---|---|---|

| Name  | LVDEN |   |   |   |   |   |   |   |

| Туре  | R/W   | R | R | R | R | R | R | R |

| Reset | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xCB; SFR Page = 0 Bit 7: Low voltage detector enable bit.

0: Disable

1: Enable

\*PS: In Sleep Mode, Low voltage occur than Wake-up MCU.

#### LVDCR1: LVD Control Register 1

| Bit   | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---|---|---|---|---|---|---|

| Name  | LVDSF |   |   |   |   |   |   |   |

| Туре  | R/W   | R | R | R | R | R | R | R |

| Reset | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xCC; SFR Page = 0

Bit 7: Low Voltage Detector Status Flag.

#### 7.5 Operation Mode Structure

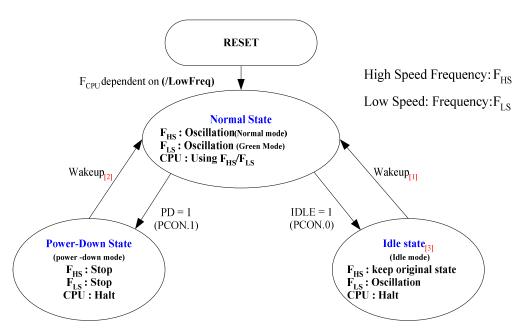

The EM85F684A/EM85F682A supports three states: Normal State, Idle State and Power-Down state. In normal state, system clock can be used high-speed clock (Normal Mode) or low-speed oscillator (Green Mode) to reduce power consumption

Figure 7.5.1 presents the operation state structure in EM85F684A/EM85F682A. Definition 7.5.1 describes the Power Control Register (PCON) used to control the EM85F684A/EM85F682A Power-down and Idle power management modes.

Figure 7.5.1 Operation Mode Structure

- [1]. Any enable interrupt source or reset.

- [2]. External interrupts, Pin change, POR, WDT, USB, etc.

- [3].CPU is halt, but system clock does not stop.

#### 7.5.1 Normal/Green Mode

In normal/green mode, CPU and peripherals continue to execute. When setting the LowFreqB (CKCON1.0), it will cause the controller core to enter low-speed oscillator (green mode).

Setting LowFreqB (CKCON1.0) allows System clock to switch between high speed and low speed. When the LowFreqB is set to "0", F<sub>HS</sub> oscillator source is automatically stopped. When the LowFreqB is set to "1", the System clock will switch to F<sub>HS</sub>.

#### Normal / Green Mode Features:

- 1. All analog and digital peripheral remains active.

- 2. System clock can choose to operate at high speed (normal mode) or low-speed mode (green mode)

#### 7.5.2 Idle Mode

Setting the Idle mode select bit (PCON.0) entering the mode, this mode will stop the CPU. However the digital and analog peripherals continue to operate. In this mode, all of enabled Interrupt and Reset can wake up.

#### Idle Mode Features:

- 1. The CPU is halt, all analog and digital peripheral remains active.

- 2. CPU can wake up by Reset or any enabled Interrupt.

- 3. RAM and SFR contents remain unchanged.

#### 7.5.3 Power-Down Mode

Setting the Power-Down mode select bit (PCON.1) can enter this mode. In this mode, the CPU and the digital peripheral will halt automatically. (Except INT, WDT, and except USB, if these function are enabled.)

#### **Power-Down Mode Features:**

- The CPU, analog and digital peripheral stop (Exceptions: INT, Pin-change, WDT and USB function. These functions / interrupts remain active if they are enabled before entering power down mode.)

- 2. When WDT is enabled,  $F_{LS}$  will not stop and will cause WDT Timeout reset.

#### Wakeup Source:

- 1. WDT timeout (WDTE = 1)

- 2. Pin-change interrupt is enabled (including INT0 and INT1).

- 3. When Power on reset occurs.

- 4. When I2C is enabled, and receiving a valid I2C address.

- 5. When USB is enabled and receives USB resume signal.

Note: NOP instruction must be added after Idle/ power down command.

#### 7.6 Flash Program Memory

The Flash Program Memory is the location where the user code or program is stored.

Two ways to program Flash Memory:

(1)By using ICP (ISP)

(2)By using Elan IAP Tool

Once cleared to Logic 0, a Flash bit must be erased to set it back to Logic 1. Typically, Flash bytes are erased (set to 0xFF) before being reprogrammed.

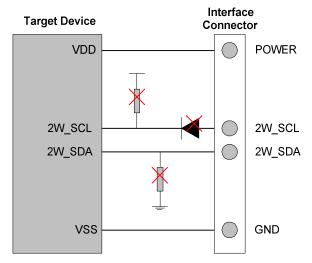

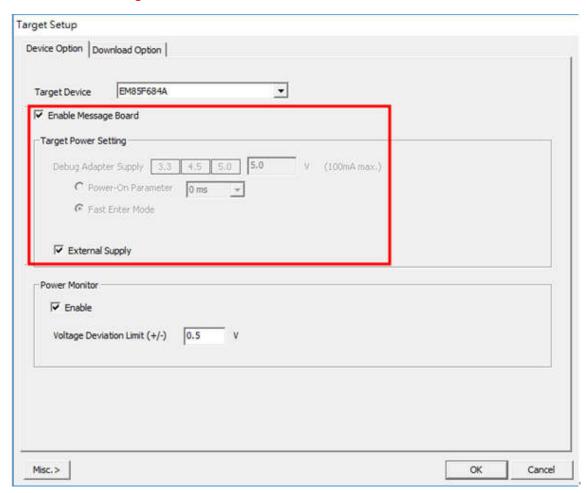

#### 7.6.1 In-Circuit Programming (ICP)

In-Circuit Programming allows programming and reprogramming the microcontroller. This is simply done with two lines for clock and data and two other lines for power and ground.

#### 7.6.2 In-Application Programming (IAP)

The EM85F684A/EM85F682A supports In-Application Programming (IAP), allowing the program memory to be modified during execution.

#### 7.7 Port Configuration

All port pins of the EM85F684A/EM85F682A may be configured in one of the two modes as follows:

(1)Output (Internal pull high automatically disconnected when switching output)

(2)Input-Only

Port modes may be assigned in software on a pin-by-pin basis as shown in Table 7.7.1 The data registers is listed in Table 7.7.2, it can set the Port Latch logic value or read the Port Pin logic state in Port cells configured for digital I/O.

I/O pins can be multiplexed with other functions. When I/O is working as other functions, changing the IOCX register value to change the I/O mode is not allowed. The corresponding register is allowed to change the I/O mode only when other functions are disabled.

**Table 7.7.1 Port Configuration Modes**

| PxM0 | Port Mode                   |

|------|-----------------------------|

| 0    | Push-Pull Output            |

| 1    | Input Only (High Impedance) |

(x = 5, 6, 7, 8, 9; y = 0, 1, 2, 3, 4, 5, 6, 7)

0: Push-Pull Output

1: Input-Only

Table 7.7.2 Port Configuration Mode 0 Registers

| Register     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------------|--------|--------|--------|--------|--------|--------|--------|--------|

| P5M0 (0xF9)  | P5M0.7 | P5M0.6 | P5M0.5 | P5M0.4 | P5M0.3 | P5M0.2 | P5M0.1 | P5M0.0 |

| P6M0 (0xFA)  | P6M0.7 | P6M0.6 | P6M0.5 | P6M0.4 | P6M0.3 | P6M0.2 | P6M0.1 | P6M0.0 |

| P7M0 (0xFB)  | P7M0.7 | P7M0.6 | P7M0.5 | P7M0.4 | P7M0.3 | P7M0.2 | P7M0.1 | P7M0.0 |

| P8M0 (0xFC)  | P8M0.7 | P8M0.6 | P8M0.5 | P8M0.4 | P8M0.3 | P8M0.2 | P8M0.1 | P8M0.0 |

| P9M0 (0xF9)* | P9M0.7 | P9M0.6 | P9M0.5 | P9M0.4 | P9M0.3 | P9M0.2 | P9M0.1 | P9M0.0 |

| Туре         | R/W    |

| Reset        | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

#### EM85F684A/EM85F682A

**USB Microcontroller**

\*:The Register P9M0 is in PAGE 1.

Table 7.7.3 Port Data Registers

| Register  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------|------|------|------|------|------|------|------|------|

| P5 (0x80) | P5.7 | P5.6 | P5.5 | P5.4 | P5.3 | P5.2 | P5.1 | P5.0 |

| P6 (0x90) | P6.7 | P6.6 | P6.5 | P6.4 | P6.3 | P6.2 | P6.1 | P6.0 |

| P7 (0xA0) | P7.7 | P7.6 | P7.5 | P7.4 | P7.3 | P7.2 | P7.1 | P7.0 |

| P8 (0xB0) | P8.7 | P8.6 | P8.5 | P8.4 | P8.3 | P8.2 | P8.1 | P8.0 |

| P9 (0xE8) | P9.7 | P9.6 | P9.5 | P9.4 | P9.3 | P9.2 | P9.1 | P9.0 |

| Туре      | R/W  |

| Reset     | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

1. When writing to the data register,

0: Set the output latch to Logic LOW,

1: Set the output latch to Logic HIGH.

2. When reading the data register,

0: Port pin is Logic LOW,

1: Port pin is Logic HIGH.

PHCON0: Pull-High Control 0

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name  | P5PH.7 | P5PH.6 | P5PH.5 | P5PH.4 | P5PH.3 | P5PH.2 | P5PH.1 | P5PH.0 |

| Туре  | R/W    |

| Reset | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

SFR Address = 0xFD; SFR Page = 0

Bits 7~0: Set these bits to enable Port 5 Pull-High.

PHCON1: Pull-High Control 1

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name  | P6PH.7 | P6PH.6 | P6PH.5 | P6PH.4 | P6PH.3 | P6PH.2 | P6PH.1 | P6PH.0 |

| Туре  | R/W    |

| Reset | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

SFR Address = 0xF5; SFR Page = 0

Bits 7~0: Set these bits to enable Port 6 Pull-High.

#### PHCON2: Pull-High Control 2

| Bit   | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|---|---|-------|-------|-------|-------|-------|-------|

| Name  |   |   | P9PH1 | P9PH0 | P8PH1 | P8PH0 | P7PH1 | P7PH0 |

| Туре  |   |   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset | 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     |

#### SFR Address = 0xFD; SFR Page = 1

Bit 5: Port 9 pull-high enable control on high nibble.

0: Disable the P9.7 ~ P9.4 pull-high

1: Enable the P9.7 ~ P9.4 pull-high

Bit 4: Port 9 pull-high enable control on low nibble.

0: Disable the P9.3 ~ P9.0 pull-high

1: Enable the P9.3 ~ P9.0 pull-high

Bit 3: Port 8 pull-high enable control on high nibble.

0: Disable the P8.7 ~ P8.4 pull-high

1: Enable the P8.7 ~ P8.4 pull-high

Bit 2: Port 8 pull-high enable control on low nibble.

0: Disable the P8.3 ~ P8.0 pull-high

1: Enable the P8.3 ~ P8.0 pull-high

Bit 1: Port 7 pull-high enable control on high nibble.

0: Disable the P7.7 ~ P7.4 pull-high

1: Enable the P7.7 ~ P7.4 pull-high

Bit 0: Port 7 pull-high enable control on low nibble.

0: Disable the P7.3 ~ P7.0 pull-high

1: Enable the P7.3 ~ P7.0 pull-high

#### PHDSC0: Port High Drive/Sink Control 0

| Bit   | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| Name  | P5PHS.7 | P5PHS.6 | P5PHS.5 | P5PHS.4 | P5PHS.3 | P5PHS.2 | P5PHS.1 | P5PHS.0 |

| Туре  | R/W     |

| Reset | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

SFR Address = 0xFF; SFR Page = 0

Bits 7~0: Set these bits to enable Port 5 High Drive/Sink.

#### PHDSC1: Port High Drive/Sink Control 1

| Bit   | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| Name  | P6PHS.7 | P6PHS.6 | P6PHS.5 | P6PHS.4 | P6PHS.3 | P6PHS.2 | P6PHS.1 | P6PHS.0 |

| Туре  | R/W     |

| Reset | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

SFR Address = 0xF7; SFR Page = 0

Bits 7~0: Set these bits to enable Port 6 High Drive/Sink.

#### PHDSC2: Port High Drive/Sink Control 2

| Bit   | 7 | 6 | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|---|--------|--------|--------|--------|--------|--------|

| Name  | - | - | P9PHS1 | P9PHS0 | P8PHS1 | P8PHS0 | P7PHS1 | P7PHS0 |

| Туре  | - | - | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Reset | 0 | 0 | 0      | 0      | 0      | 0      | 0      | 0      |

SFR Address = 0xFF; SFR Page = 1

Bit 7: Port 5 high drive/sink enable control on high nibble.

0: Disable the P5.7 ~ P5.4 high drive/sink.

1: Enable the P5.7 ~ P5.4 high drive/sink.

Bit 6: Port 5 high drive/sink enable control on low nibble.

0: Disable the P5.3 ~ P5.0 high drive/sink.

1: Enable the P5.3 ~ P5.0 high drive/sink.

Bit 5: Port 9 high drive/sink enable control on high nibble.

0: Disable the P9.7 ~ P9.4 high drive/sink.

1: Enable the P9.7 ~ P9.4 high drive/sink

- **Bit 4:** Port 9 high drive/sink enable control on low nibble.

- 0: Disable the P9.3 ~ P9.0 high drive/sink.

- 1: Enable the P9.3 ~ P9.0 high drive/sink.

- Bit 3: Port 8 high drive/sink enable control on high nibble.

- 0: Disable the P8.7 ~ P8.4 high drive/sink.

- 1: Enable the P8.7 ~ P8.4 high drive/sink.

- Bit 2: Port 8 high drive/sink enable control on low nibble.

- 0: Disable the P8.3 ~ P8.0 high drive/sink.

- 1: Enable the P8.3 ~ P8.0 high drive/sink.

- Bit 1: Port 7 high drive/sink enable control on high nibble.

- 0: Disable the P7.7 ~ P7.4 high drive/sink.

- 1: Enable the P7.7 ~ P7.4 high drive/sink.

- Bit 0: Port 7 high drive/sink enable control on low nibble.

- 0: Disable the P7.3 ~ P7.0 high drive/sink.

- 1: Enable the P7.3 ~ P7.0 high drive/sink.

#### 7.7.1 Push-Pull Output Mode

Figure 7.7.1 Push-Pull Output Mode

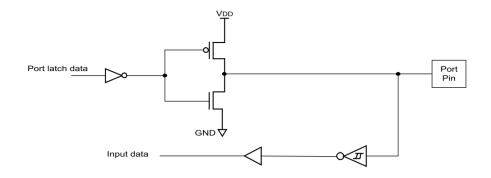

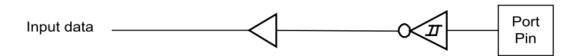

#### 7.7.2 Input-Only Mode

In Input-Only mode port is input only, no output capability. Input-Only mode port structure diagram is shown in Figure 7.7.2 Input-Only Mode.

Figure 7.7.2 Input-Only Mode

(This diagram is for reference only, based on the actual circuit design)

#### 7.8 Interrupts

EM85F684A/EM85F682A include an extended interrupt system supporting multiple interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt flag located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt flag is set to Logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt flag is ignored by the hardware and program execution continues as normal (The interrupt flag is set to Logic 1 regardless of the interrupt's enable/disable state).

Each of the interrupt sources can be individually enabled or disabled through the SFR relevant enabled interrupt. At the same time, the EA (IE.7) must also be set to "1" to activate the enabled interrupt master switch, so that each of the interrupt sources that have been enabled becomes effective. No matter what is bit setting of each enabled interrupt, clearing EA will disable all the interrupts. When CPU enters ISR, a few number of interrupt flags are automatically cleared by hardware while most of them can be cleared only with software while remaining in ISR state. If the interrupt flag setting remains at "1" after the CPU completes the return from interrupt (RETI) instruction, it will immediately generate a new interrupt request. After executing the next instruction, the CPU will then re-enter ISR.

#### 7.8.1 Interrupt Sources

All the interrupt sources are listed in Table 7.8. If Interrupt Mask is activated and an Interrupt Source occurs, the system will generate an interrupt request and set the Interrupt Flag, the CPU will jump to the address corresponding to the ISR (Interrupt Vector), not through the hardware automatically cleared Interrupt Flag, must use software manually cleared.

| Priority<br>Order | Interrupt<br>Vector | Interrupt<br>Source           | Interrupt<br>Flag                                                                                                                                                                                                                                        | Clear<br>by HW | Interrupt<br>Mask  |

|-------------------|---------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|

| Тор               | 0x0000              | Reset                         | None                                                                                                                                                                                                                                                     | N/A            | Always<br>Enabled  |

| 0                 | 0x0003              | External Interrupt 0 INT0     | IE0 (TCON.1)                                                                                                                                                                                                                                             | Υ              | EX0 (IE.0)         |

| 1                 | 0x000B              | Timer 0 Overflow              | TF0 (TCON.5)                                                                                                                                                                                                                                             | Υ              | ET0 (IE.1)         |

| 2                 | 0x0013              | External Interrupt 1 INT1     | IE1 (TCON.3)                                                                                                                                                                                                                                             | Υ              | EX1 (IE.2)         |

| 3                 | 0x001B              | Timer 1 Overflow              | TF1 (TCON.7)                                                                                                                                                                                                                                             | Υ              | ET1 (IE.3)         |

| 4                 | 0x0023              | UART                          | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                                                                                                                                                                                                           | N              | ES0 (IE.4)         |

| 5                 | 0x002B              | -                             | -                                                                                                                                                                                                                                                        | -              | -                  |

| 6                 | 0x0033              | Pin Change<br>Interrupt       | IC5SF (ICEN.0)<br>IC6SF (ICEN.1)<br>IC9SF (ICEN.3)                                                                                                                                                                                                       | N              | ICIE (IE.6)        |

| 7                 | 0x003B              | LVD                           | LVDSF (LVDCR1.7)                                                                                                                                                                                                                                         | N              | LVDIE(EIE1.0)      |

| 8                 | 0x0043              | System-Hold                   | SHSF (PSW1.0)                                                                                                                                                                                                                                            | N              | SHIE (EIE1.1)      |

| 9                 | 0x004B              | -                             | -                                                                                                                                                                                                                                                        | -              | -                  |

| 10                | 0x0053              | External Interrupt 2~3 INT2~3 | EXSF2 (EEXSF.0)<br>EXSF3 (EEXSF.1)                                                                                                                                                                                                                       | N              | EEXIE<br>(EIE1.3)  |

| 11                | 0x005B              | SPI                           | SPISF (SPISR2.7)                                                                                                                                                                                                                                         | N              | SPIE (EIE1.4)      |

| 12                | 0x0063              | PWMD                          | PWMDDSF (PWMSF1.0)<br>PWMDPSF (PWMSF1.1)                                                                                                                                                                                                                 | N              | PWMDIE<br>(EIE1.5) |

| 13                | 0x006B              | -                             | -                                                                                                                                                                                                                                                        | -              | -                  |

| 14                | 0x0073              | Timer 3                       | TC3SF(TC3CR1.4)                                                                                                                                                                                                                                          | N              | TCIE(EIE1.7)       |

| 15                | 0x007B              | PWMA                          | PWMADSF (PWMSF.0)<br>PWMAPSF (PWMSF.1)                                                                                                                                                                                                                   | N              | PWMAIE<br>(EIE2.0) |

| 16                | 0x0083              | PWME                          | PWMEDSF (PWMSF1.2)<br>PWMEPSF (PWMSF1.3)                                                                                                                                                                                                                 | N              | PWMDIE<br>(EIE2.1) |

| 17                | 0x008B              | USB                           | SOFSF (UDCINTOSTA.7) SUSPSF (UDCINTOSTA.6) RSTSF (UDCINTOSTA.5) LPMRESSF (UDCINTOSTA.4) RESSF (UDCINTOSTA.3) SETUPSF (UDCINTOSTA.1) EXTPKGSF(UDCINTOSTA.0) EP3OUTSF (UDCINT1STA.7) EP3INSF (UDCINT1STA.6) EP2OUTSF (UDCINT1STA.5) EP2INSF (UDCINT1STA.4) | N              | USBIE<br>(EIE2.2)  |

|    |                | 1        |                         |    | <u> </u>                              |

|----|----------------|----------|-------------------------|----|---------------------------------------|

|    |                |          | EP10UTSF                |    |                                       |

|    |                |          | (UDCINT1STA .3)         |    |                                       |

|    |                |          | EP1INSF (UDCINT1STA.2)  |    |                                       |

|    |                |          | EP0OUTSF (UDCINT1STA.1) |    |                                       |

|    |                |          | EP0INSF (UDCINT1STA.0)  |    |                                       |

|    |                |          | EP4INEMPSF              |    |                                       |

|    |                |          | (UDCINT2STA.7)          |    |                                       |

|    |                |          | EP3INEMPSF              |    |                                       |

|    |                |          | (UDCINT2STA.6)          |    |                                       |

|    |                |          | EP2INEMPSF              |    |                                       |

|    |                |          | (UDCINT2STA.5)          |    |                                       |

|    |                |          | EP1INEMPSF              |    |                                       |

|    |                |          | (UDCINT2STA.4)          |    |                                       |

|    |                |          | EP0INEMPSF              |    |                                       |

|    |                |          | (UDCINT2STA.3)          |    |                                       |

|    |                |          | EP4OUTSF (UDCINT2STA.3) |    |                                       |

|    |                |          | EP4INSF (UDCINT2STA.2)  |    |                                       |

|    |                |          | ERRSF(UDCINT2STA.0)     |    |                                       |

| 40 | 0.0000         | DIAMAE   | PWMFDSF (PWMSF1.4)      |    | PWMEIE                                |

| 18 | 0x0093         | PWMF     | PWMFPSF (PWMSF1.5)      | N  | (EIE2.3)                              |

| 19 | 0x009B         | -        | -                       | 1  | -                                     |

|    |                |          | I2CATSF (I2CASF.0)      |    | I2CAIE                                |

| 20 | 0x00A3         | I2CA     | I2CARSF (I2CASF.1)      | Ν  |                                       |

|    |                |          | I2CASTPSF (I2CASF.2)    |    | (EIE2.5)                              |

| 21 | 0x00AB         | -        | -                       | -  | -                                     |

| 22 | 0x00B3         | -        | -                       | -  | -                                     |

| 23 | 0x00BB         | PWMB     | PWMBDSF (PWMSF.2)       | N  | PWMBIE                                |

| 23 | UXUUDD         | FVVIVID  | PWMBPSF (PWMSF.3)       | IN | (EIE3.0)                              |

| 24 | 0x00C3         | PWMC     | PWMCDSF (PWMSF.4)       | N  | PWMCIE                                |

| 24 | 0,0000         | 1 VVIVIC | PWMCPSF (PWMSF.5)       | IN | (EIE3.1)                              |

| 25 | 0x00CB         | -        | -                       | -  | -                                     |

| 26 | 0x00D3         | -        | -                       | •  | -                                     |

| 27 | 0x00DB         | -        | -                       | -  | -                                     |

|    |                |          | I2CBTXSF(I2CBINT.7)     |    |                                       |

|    |                |          | I2CBRXSF (I2CBINT.6)    |    |                                       |

| 20 | 0,000          | IOCE     | I2CBSTPSF (I2CBINT.4)   | N  | I2CBIE                                |

| 20 | 28 0x00E3 I2CB | IZUD     | TO1SF (SMbusTO1.6)      | IN | (EIE3.5)                              |

|    |                |          | TO2SF (SMbusTO2.6)      |    |                                       |

|    |                |          | TO3SF (SMbusTO3.6)      |    |                                       |

|    |                |          |                         |    | · · · · · · · · · · · · · · · · · · · |

Table 7-9 Interrupt Sources

## IE: Interrupt Enable

| Bit   | 7   | 6    | 5 | 4   | 3   | 2   | 1   | 0   |

|-------|-----|------|---|-----|-----|-----|-----|-----|

| Name  | EA  | ICIE | - | ES0 | ET1 | EX1 | ET0 | EX0 |

| Type  | R/W | R/W  | R | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0    | 0 | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xA8; SFR Page = All Pages

Bit 7: Enable All Interrupts

Globally enables/disables all interrupts. It overrides individual interrupt mask settings.

0: Disable all interrupt sources.

1: Enable each interrupt according to its individual mask setting.

Bit 6: Input-Change Interrupt

This bit sets the masking of the Pin Change interrupt.

0: Disable Pin Change interrupt.

1: Enable Pin Change interrupt.

Bit 5: Reserved

Bit 4: Enable UART Interrupt

This bit sets the masking of the UART interrupt.

0: Disable UART interrupt.

1: Enable UART interrupt.

Bit 3: Enable Timer 1 Interrupt.

This bit sets the masking of the Timer 1 interrupt.

0: Disable all Timer 1 interrupt.

1: Enable Interrupt requests generated by the TF1 flag.

Bit 2: Enable External Interrupt 1.

This bit sets the masking of External Interrupt 1.

0: Disable external Interrupt 1.

1: Enable Interrupt requests generated by the INT1 input.

Bit 1: Enable Timer 0 Interrupt

This bit sets the masking of the Timer 0 interrupt.

0: Disable all Timer 0 interrupt.

1: Enable Interrupt requests generated by the TF0 flag.

Bit 0: Enable External Interrupt 0.

This bit sets the masking of External Interrupt 0.

0: Disable external Interrupt 0.

1: Enable Interrupt requests generated by the INT0 input.

#### **EIE1: Extended Interrupt Enable 1**

| Bit   | 7    | 6 | 5      | 4     | 3     | 2 | 1    | 0     |

|-------|------|---|--------|-------|-------|---|------|-------|

| Name  | TCIE | - | PWMDIE | SPIIE | EEXIE | - | SHIE | LVDIE |

| Туре  | R/W  | R | R/W    | R/W   | R/W   | R | R/W  | R/W   |

| Reset | 0    | 0 | 0      | 0     | 0     | 0 | 0    | 0     |

SFR Address = 0xB1; SFR Page = Page 0

Bits 6, 2: Reserved

Bit 7: Timer 3 Overflow Interrupt Enable.

0: Disable Timer 3 Overflow Interrupt

1: Enable Timer 3 Overflow Interrupt

Bit 5: PWMD Interrupt Enable.

This bit sets the masking of the PWMD interrupt.

0: Disable PWMD interrupt.

1: Enable PWMD interrupt

Bit 4: Serial Peripheral Interface (SPI) Interrupt Enable.

This bit sets the masking of the SPI interrupt.

0: Disable SPI interrupt.

1: Enable SPI interrupt

Bit 3: Extended External Interrupt Enable (INT2~3).

This bit sets the masking of the Extended External interrupt.

0: Disable Extended External interrupt.

1: Enable Extended External interrupt

Bit 1: System-Hold Interrupt Enable.

This bit sets the masking of the System-Hold interrupt.

0: Disable System-Hold interrupt.

1: Enable System-Hold interrupt

Bit 0: Low Voltage Detector (LVD) Interrupt Enable.

This bit sets the masking of the LVD interrupt.

0: Disable LVD interrupt.

1: Enable LVD interrupt

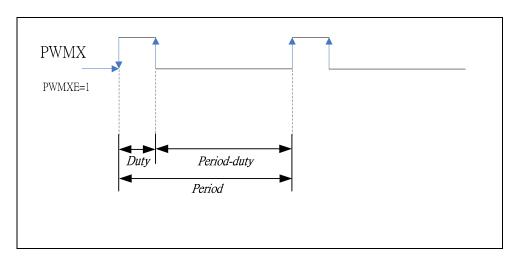

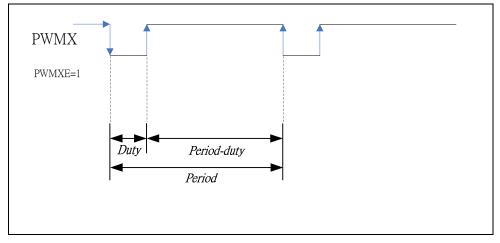

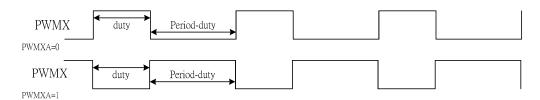

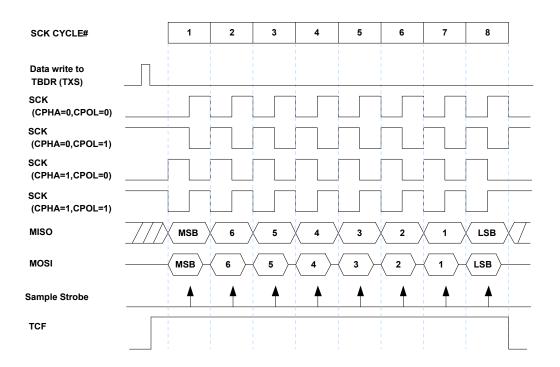

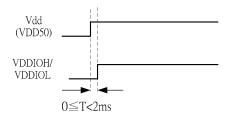

#### **EIE2: Extended Interrupt Enable 2**